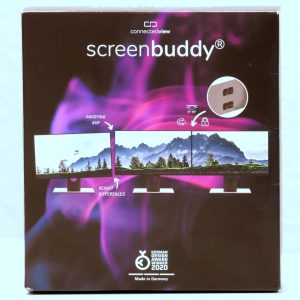

Verpackung und Lieferumfang Für den Fall, dass man zwischen Kauf und Erhalt der NAS vergessen hat, wer sie hergestellt hat, wird der Name nochmal auf jeder Seite des Kartons aufgedruckt. Sehr hilfreich! Der Inhalt wird durch passend zugeschnittene Blöcke aus Schaumstoff geschützt, seitlich befindet sich noch zusätzlich eine Box mit dem Zubehör [...]

Endorfy Fera 5 Black Luftkühler im Test – Altes Modell mit neuem Anstrich